Microelectronics Research Development Corporation

KM-805510; Temporal LatchTM SEU Immune Programmable FPGA Scrubber

White Paper: "Fast Local Scrubbing for FPGA’s Configuration Memory"

Electronic integrated circuits providing radiation hardening for digital logic architecture

Scrubbing is the process of removing errors from a memory's content by rewriting it periodically with correct values. Scrubbing is used in conjunction with Triple Mode Redundancy (TMR) to mitigate the effects of radiation in SRAM-based FPGAs. Micro-RDC's programmable scrubber for FPGAs is the first industry available scrubber flexible enough to support a wide range of FPGA families and different implementation options (Radiation-Hardened-By-Design (RHBD) Structured ASIC (S-ASIC) or RTL for implementation in any reconfigurable device). RTL can be implemented in any generic FPGA.

Features

- Based on a RISC processor with 8-bit data bus and 14-bit wide instructions, up to 64K instructions and a operation frequency of 50MHz.

- CRC16 calculation capability for error detection. Stores up to 1024 checksums.

- Error Detection And Correction (EDAC) optional.

- Frame-based scrubbing capable.

- Read-detect-scrub capable.

- Single Event Failure Interrupt (SEFI) detection capabilities.

- Capable of fully configuring the device upon request.

- Supports SelectMAP32, SelectMAP8, ICAP32 and JTAG configuration interfaces.

- Expandable to interface with different forms of non-volatile storage.

- Reporting and statistics gathering capabilities through a RS232 port.

- Modular design: Can add or remove peripherals as needed. Basic module comprises the RISC controller, a Read Only Memory (ROM) interface, a CRC16 calculation module, a communication module (RS232) and a configuration memory interface (SelectMAP32).

- Available in IP form (to be implemented in a reconfigurable device) or in a Rad-Hard S-ASIC device.

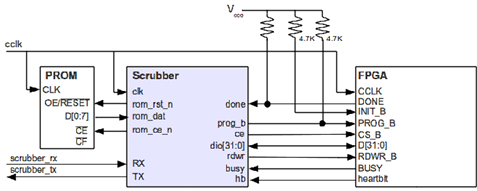

Scrubber as Master Configuration Controller

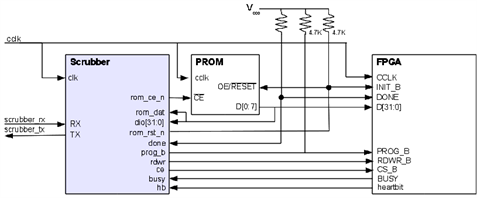

Scrubber as Slave Configuration Controller