Microelectronics Research Development Corporation

RHBD; Temporal LatchTM SEU Immune 90nm CMOS Structured ASIC

Electronic integrated circuits providing radiation hardening for digital logic architecture

Features

- Single-Layer-Configurable

- IBM 9LP 90nm CMOS Technology

- Temporal Latch Technology for SEU Immunity

- Hardness Estimate: TID > 1Mrad(Si), SEU < 1e-8 Errors/day, SEL > 75 MeV-cm2/mg (LET)

- Design-Hardened Fabric w/Distributed Dual-Port SRAM (Logic Cell w/Memory in Each Tile)

- Logic Based on Hardened Adjustable Temporal Latch w/Delay Control -> SEU Immunity

- Design-Hardened PLL; Input Frequency: 10MHz to 125MHz

- Design-Hardened 1.25 Gbps LVDS Channels; Input Frequency: 75 MHz to 125 MHz

- Design-Hardened Configurable 8K X 8 SRAM Memory Blocks w/EDAC

- Design-Hardened Via-Configurable ROM

- Design-Hardened Via-Configurable IO

- Dual Voltage Supply; 1.2V Core and 1.8V to 2.5V IO

Structured ASIC Benefits

- Advantages over FPGA

- Advantages over Custom ASIC

- Superior to TTL/COTS

- Low Development and Fabrication Costs

- Reduced Design Development and Fabrication Time

- "Trusted Capabilities"

- Excellent Performance Characteristics

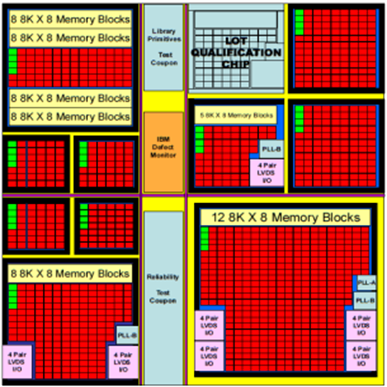

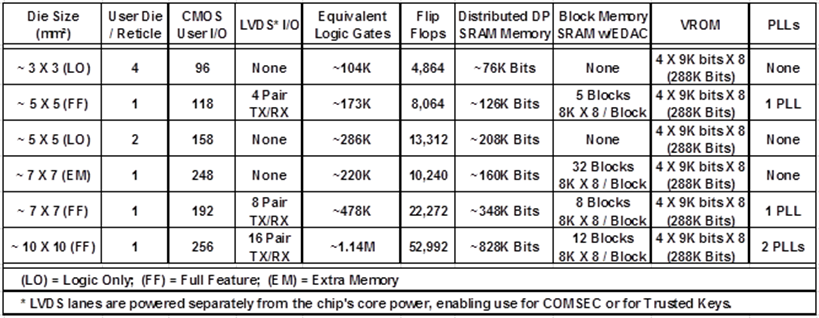

6 Different Die Configurations

Available for Customer Personalizations:

Available for Customer Personalizations:

4 = ~3mm x ~3mm die

3 = ~5mm x ~5mm die (2 styles)

2 = ~7mm x ~7mm die (2 styles)

1 = ~10mm x ~10mm die

3 = ~5mm x ~5mm die (2 styles)

2 = ~7mm x ~7mm die (2 styles)

1 = ~10mm x ~10mm die

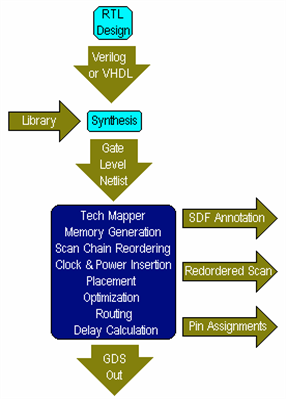

One-layer programmability delivers low-costs, reduced design hours and rapid cycle time.

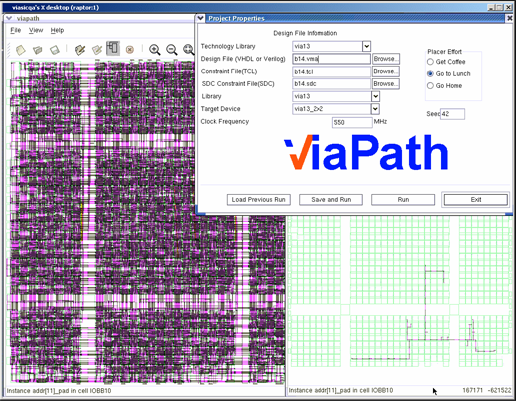

ViASIC/Triad's ViaPath place and route software converts a VHDL/Verilog design into a Design-Hardened Structured ASIC.