Microelectronics Research Development Corporation

KM-807701; Temporal LatchTM SEU Immune RHBD 90nm CMOS 8051XC Based SoC

Electronic integrated circuits providing radiation hardening for digital logic architecture

Specifications:

8051XC CPU

8051XC CPU

- 50 MHz Clock

- Average 8x Speed Up Over Standard 8051

- ALU Performs 8-bit Arithmetic, Multiplication and Division, and Boolean Manipulations

- Write to Program Memory RAM

- Two 8 bit I/O Ports (32 lines)

- Two 8 bit Bi-Directional Ports

- Three 16-bit Timer/Counters

- Real Time Clock (RTC)

- Watch Dog Timer

- 8 External Interrupts

- SEU Immune by Incorporating Temporal Latch Technology in all Sequential Logic

- On Chip Internal RAM (256x8)

- Temporal Latch Based Flip Flops

- On Chip External 12 Kbytes Data RAM Design Hardened Distributed SRAM

- On Chip 64 KBytes Program RAM

- Bootup from External SPI EEPROM

- Design Hardened 64Kx8 Program SRAM w/EDAC

- On Chip ROM for Testing and Bootup

- SPI Slave for Firmware Download and Upload to Silicon

- Support for 128 Kbytes External SPI Non Volatile Memory

- Idle and Deep Sleep

- Power Pins (Do Not Change in Idle or Deep Sleep or Reset)

- UART with FIFO and CTS/RTS DTR/DCD Support

- Four Serial Ports with Independent Baud Rate Generators

- USB 1.1 Host/Slave Controller

- Spacewire Multiple Rates Including 10 Mbps and 50 Mbps

- LVDS Driver/Receiver for Spacewire

- I2C Primary Master

- I2C Secondary Master

- SPI Master with 8 Slave Selects

- SPI Slave

- Test Bypass

- CRC Accelerator

- PWM

- PPS Input (Pulse Per Second)

- 7.004 mm X 7.324 mm

- 380 Pins, 192 CMOS I/O

- 64 um pad pitch

- 50 um X 50 um pad size

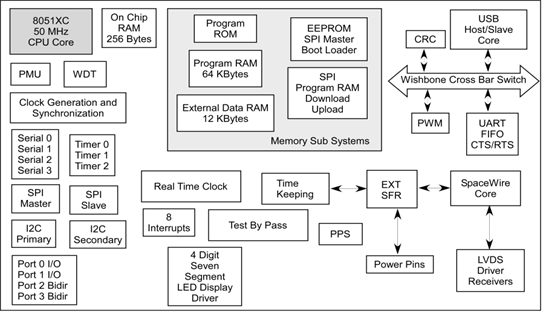

Block Diagram

LGA-484 Evaluation Chip

RHBD IBM 9LP 90nm CMOS

- Total Ionizing Dose: Within specifications after exposure to greater than 1Mrad(Si)

- Single Event Latch Up: Latchup immune to 80 MeV-cm2/mg

- SRAM Error Rate: Supports scrubbing program SRAM to obtain desired error rates

- Single Event Transient: Implements the Temporal Latch-based flip flops to mitigate transient pulse widths of up to 1ns

This effort is sponsored by the Air Force Research Laboratory (AFRL).